This list is; you can help. XC-series ModelLaunchXC20641985XC30201988XC40001991XC31001992XC32001992XC50001994XC81001995XC62001995Spartan ModelLaunchSpartan1998Spartan-II2000Spartan-3E2005Spartan-3A2007Spartan-62009Spartan-72017 ModelLaunchVirtex1998Virtex-E1999Virtex-EM2000Virtex-II2001Virtex-IV2005Virtex-52006Virtex-62009Virtex-72010Virtex UltraScale2013Virtex UltraScale+2015Artix ModelLaunchArtix-72010Kintex ModelLaunchKintex-72010Kintex UltraScale2013Kintex UltraScale+2015References. Akthar, Shahul (2014-09-21). All About FPGA. Retrieved 2018-12-03.

(PDF). Retrieved 2018-12-03. (PDF).

Retrieved 2018-11-28. ^. Retrieved 2018-12-03. Maxfield, Clive. Retrieved 2018-11-30.

(PDF). Retrieved 2018-11-28. Retrieved 2018-12-03. Retrieved 2018-12-03. (PDF). Retrieved 2018-12-03.

Merritt, Rick (2018-10-03). EE Times Asia. Retrieved 2018-12-03. Leibson, Steven (2018-10-11). Retrieved 2018-12-03. Lazzaro, John. Retrieved 2018-12-03.

^. Retrieved 2018-12-03. ^. Retrieved 2018-12-03.

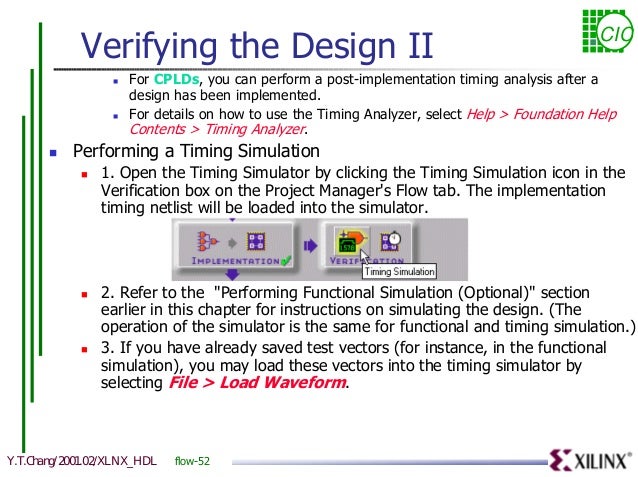

Xilinx ISE TutorialXilinx ISE Foundation TutorialThis is a brief tutorial for the Xilinx ISEFoundation Software. It targets first-time users who want to getstarted with the ISE Foundation Software to synthesize a digitaldesign. During the course of the tutorial, all steps of thesynthesis process are covered using a half-adder as runningexample.

We start with the input of the circuit in the schematiceditor, simulate the timing behavior of the circuit, compile it for aVirtex-4 FPGA, and test the design on an ML405 prototypingboard.This tutorial is for the ISE FoundationSoftware, Version 8.2i. Screen dumps have been generated fromthat version on a Linux system.The tutorial contains the following steps:.The following sections provide additional information:provides pointers to online manualsThis tutorial is accompanied by the followingsections that are also linked at the top of this page:. (Advanced: readwhen you're ready to move on beyond the windows interface)1 Project Manager: How toCreate a New ProjectStart the ISE Project Navigator, calledise on Linux systems. Pulldown the File menu and click onNew Project.

Xilinx Foundation 3.1 Free

A new windowentitled ``New Project Wizard' appears. The state of affairs isshown in below.Figure 1: Project Navigator window with popup windowfor New ProjectSelect a directory for the ProjectLocation in the New Project Wizard window.

Then, inthe Project Name field, type``adder.' ' Note that the project name is added automagically tothe directory path. Finally, select Source Type ``Schematic', and clickNext. The Project Wizardswitches to the ``Device Properties' window. Select devicefamilyVirtex4 and deviceXC4VFX20, as shown inbelow.Figure 2: Project Navigator window with popup windowfor Device PropertiesClick Next a couple of times, andFinish to exit the New ProjectWizard.Now, a new project hierarchy is generated and is displayed in the``Sources Window' portion in the top left corner of the ProjectNavigator window shown in. Itcontains the directory ``adder', and the entry ``xc4vf.'

'.Note that a project is no more than a collection of files in thedirectory that you chose in theProject Location of. You can browse through thatdirectory by selecting theOpen Project item in the File menu of the Project Navigator.Figure 3: Project Navigator window with new adder project.We are now ready to create a schematic for our half-adder.2 Schematic Editor: Howto Create a SchematicIn the ``Processes' window of the ProjectNavigator, cf., double click on theentry entitled Create NewSource. (Alternatively, pulldown the Project menu and click onNew Source.) Selectsource type Schematic and enter inFile name ``halfadder', as shownin below.Figure 4: Project Navigator with popup window toSelect Source Type.Click Nextand Finish. The Project Navigatorwindow now shows the ``Design Summary' of the Schematic Editor, see. To switch to the drawing areaof the Schematic Editor click on the halfadder.sch tab at the bottom of the``Workspace' window. Later in the design process, clicking onthat file name in the Project Manager will automatically start up theSchematic Editor.Figure 5: Project Navigator window after launching the schematic editor.Note the action of having launched the SchematicEditor is logged in the Transcript portion at the bottom of theProject Navigator window.The design of the half-adder that we are aboutto generate is shown in the Schematic Editor window in.Figure 6: Schematic Editor window with half-adder schematicA schematic is generated by inserting gates and input/outputpads.

The inputs and outputs of the gates and pads are connected by meansof wires. Standard symbols such as the inverter ``inv', the and-gate``and2', and the or-gate ``or2' can be found in the ``Symbol Browser'.The Symbol Browser is opened by pulling down the Add menu and selecting Symbol. Alternatively, thehorizontal toolbar offers a button showing a gate symbol above a resistor.The ``Symbol Browser' appears to the left of the Schematic editor.Adjust the size of the ``Categories' and ``Symbols' portions of the window.A screen dump of the Project Navigator with the Symbol Browseris shown in below.Figure 7: Symbol Browser (left) and Schematic Editor (right)The symbol browser organizes symbols bycategory. Select category Logic, and scroll through the list ofcombinational gates in the list of Symbols.

According to thenaming convention in the symbol browser, gates are listed by a (sortof) descriptive name, such as ``and' or ``or'. Most names endwith a number, often describing the number of inputs (fan-in) of thegate. For example, an AND-gate with two inputs and one output isnamed ``and2'. Analogously, the name for an or-gate with twoinputs and one output is ``or2'. Gates with a single inputdon't have the number of inputs appended to the name, as for examplefor the inverter, which is simply named ``inv'.

You may inserta gate in the drawing area of the Schematic Editor by left-clicking onthe name in the Symbols list, and by moving the cursor into thedrawing area. The symbol for the gate appears attached to thecursor. Moving the mouse drags the gate across the drawingarea. Left-clicking the mouse in the drawing area causes thegate symbol to be inserted at the current mouse position.

Thisprocess can be repeated until all gates are positioned approximatelywhere they are intended to end up. Shows the gates dropped for the half-adder.Figure 8: Schematic Editor window with gates for half-adderYou can move the gates around by selecting themwith a left-click and dragging them across the drawing area.Releasing the left mouse button drops the gate at the current mouseposition. It is often convenient to change the size of thedrawing area by zooming. In wehave zoomed into the drawing area (via the View menu) to enlarge the symbols.The grid appears automatically, if you zoom in far enough.Symbols snap to the grid, which simplifies alignment.The next step is to wire up the circuit.To enter the ``Draw Wires' mode, pull down the Add menu and select the Wire item. Alternatively, there isalso an ``Add wire' button in the horizontal toolbar above thedrawing area. Then, left-click to define one end of the wire,hold the left mouse button, and release it or left-click again at theother end.

The wire is automatically routed in Manhattanstyle. Insert all wire connections as shown in. You can leave the ``Draw Wires' mode byhitting the ESC-button of your keyboard.Figure 9: Schematic Editor window after adding wires.The last step is to add input/output pads to ourcollection of gates. Pull down the Add menu and select I/O Marker.

Then, click on thefloating ends of the unconnected wires. Upon each click, a padsymbol appears. We are left with determining the direction,input or output, and the name for each of the pads. Double-clickon a pad, and a windowNet Attributes pops up.Assign the names A and B to the input pads andSUM and CARRY to the output pads as shown in above to complete the half-adderschematic. Save the design by selecting Save in the File menu.3Simulator: How to Simulate a CircuitConfigure the simulator by selecting Behaviorial Simulation in the Sources For pull-down menu of the Sourcestab of the Project Navigator, cf.Figure 10: Preparing for Behavioral Simulation.Next, we create a testbench using the WaveformGenerator. Pull down the Project menu and select New Source. Select TestBench Waveform as source, and enterFile name ``halfaddertb', cf. Click Next twice, and Finish to enter the ``Initial Timing andClock Wizard.